fm101

Member level 5

Hi,

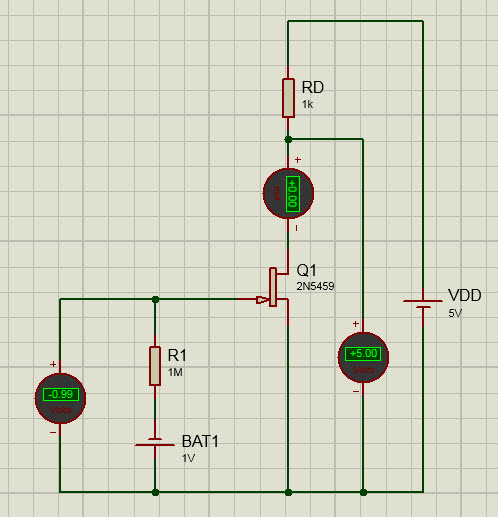

I have the following 2N5459 JFET fixed biased circuit in proteus as shown below. I calculated drain current Id and drain voltage Vd but the circuit simulation does not show the expected values. I am not sure whether my calculation is correct or it is proteus.

I took Vgs(off)=Vp=-2V with Idss=4mA which are minimum values from 2N5459 datasheet. With applied Vgs=-1V, Vdd=5V and using transconductance equation Id=Idss(1-Vgs/Vp)^2 gives Id=1mA and with Vd=Vdd-Id*Rd gives Vd=5V-(1mA)(1kOhm)=4V but the simulation shows Id=0 and Vd=5V.

Is this not the way to bias JFET?

I have the following 2N5459 JFET fixed biased circuit in proteus as shown below. I calculated drain current Id and drain voltage Vd but the circuit simulation does not show the expected values. I am not sure whether my calculation is correct or it is proteus.

I took Vgs(off)=Vp=-2V with Idss=4mA which are minimum values from 2N5459 datasheet. With applied Vgs=-1V, Vdd=5V and using transconductance equation Id=Idss(1-Vgs/Vp)^2 gives Id=1mA and with Vd=Vdd-Id*Rd gives Vd=5V-(1mA)(1kOhm)=4V but the simulation shows Id=0 and Vd=5V.

Is this not the way to bias JFET?