doenisz

Junior Member level 2

Hi guys,

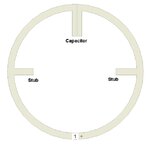

I am currently designing a circular loop antenna to be matched to the input impedance of the rectifier, at 3.5GHz. I did HFSS simulations to verify the impedance of the antenna plus the bondwires, and I used Cadence Post-Layout simulations to find the input impedance of the chip itself.

Basically, at 3.5GHz, the input impedance of the chip is like 0.7-j270, and the antenna+bondwire is 1.5+j270. For context, I'm following the methodology described here: https://ieeexplore.ieee.org/document/7435352

However, due to the other secondary effects I cannot control, they may not be matched at 3.5GHz and my chip does NOT have a control loop to adjust the resonance.

I can change some of the antenna geometrical parameters by cutting some traces etc. but I'll probably need a drilling machine. However, my antenna will be very close to the die (to reduce bondwire, transmission line and loss effects) so drilling machine may cause my wirebonds to fail.

I can always find the resonance frequency and then order new PCBs as a trial and error but wirebonding new dies to the new PCBs would cause a lot of time wasted and money too.

So, I would like to ask, in case I find that the resonance occurs at a higher or lower frequency that 3.5GHz, what can I do to tune this resonance? I also thought of using a varactor to tune the input reactance of the antenna but I was wondering how it would change the radiation efficiency?

Thanks.

I am currently designing a circular loop antenna to be matched to the input impedance of the rectifier, at 3.5GHz. I did HFSS simulations to verify the impedance of the antenna plus the bondwires, and I used Cadence Post-Layout simulations to find the input impedance of the chip itself.

Basically, at 3.5GHz, the input impedance of the chip is like 0.7-j270, and the antenna+bondwire is 1.5+j270. For context, I'm following the methodology described here: https://ieeexplore.ieee.org/document/7435352

However, due to the other secondary effects I cannot control, they may not be matched at 3.5GHz and my chip does NOT have a control loop to adjust the resonance.

I can change some of the antenna geometrical parameters by cutting some traces etc. but I'll probably need a drilling machine. However, my antenna will be very close to the die (to reduce bondwire, transmission line and loss effects) so drilling machine may cause my wirebonds to fail.

I can always find the resonance frequency and then order new PCBs as a trial and error but wirebonding new dies to the new PCBs would cause a lot of time wasted and money too.

So, I would like to ask, in case I find that the resonance occurs at a higher or lower frequency that 3.5GHz, what can I do to tune this resonance? I also thought of using a varactor to tune the input reactance of the antenna but I was wondering how it would change the radiation efficiency?

Thanks.