Junus2012

Advanced Member level 5

dear friends

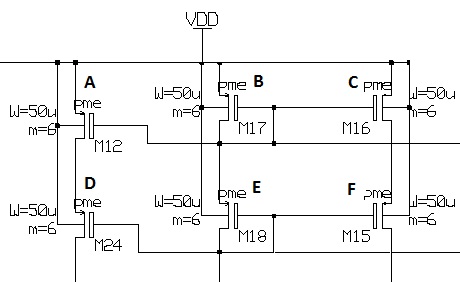

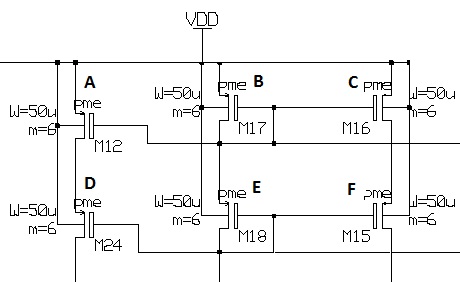

I am new in the layout design , it is the first time for me to start doing the layout. I attached you the picture of a current current mirror which I would first start with it, later on I will submit the other circuits and I really need your help and support

I am planning to have common centroid layout (cross-coupledpair). In the book of the " Art of analog design" he has gave the example of two mos transistors A and B. but in my circuit I attached I have six transistors (A,B,C,D,E,F) with the sizes you see and I dont know how to do the square array of this circuit and this what I want you to help

please keep in your mind that I can go more for higher transistors ratios but never less for the consideration of my main circuit. and also the length is fixed by the technology and I cannot alter it, so the only thing you can change is the width and the number of fingers

thank you very much and I will appreciate any participation of you

I am new in the layout design , it is the first time for me to start doing the layout. I attached you the picture of a current current mirror which I would first start with it, later on I will submit the other circuits and I really need your help and support

I am planning to have common centroid layout (cross-coupledpair). In the book of the " Art of analog design" he has gave the example of two mos transistors A and B. but in my circuit I attached I have six transistors (A,B,C,D,E,F) with the sizes you see and I dont know how to do the square array of this circuit and this what I want you to help

please keep in your mind that I can go more for higher transistors ratios but never less for the consideration of my main circuit. and also the length is fixed by the technology and I cannot alter it, so the only thing you can change is the width and the number of fingers

thank you very much and I will appreciate any participation of you