Bjtpower

Full Member level 5

Hi,

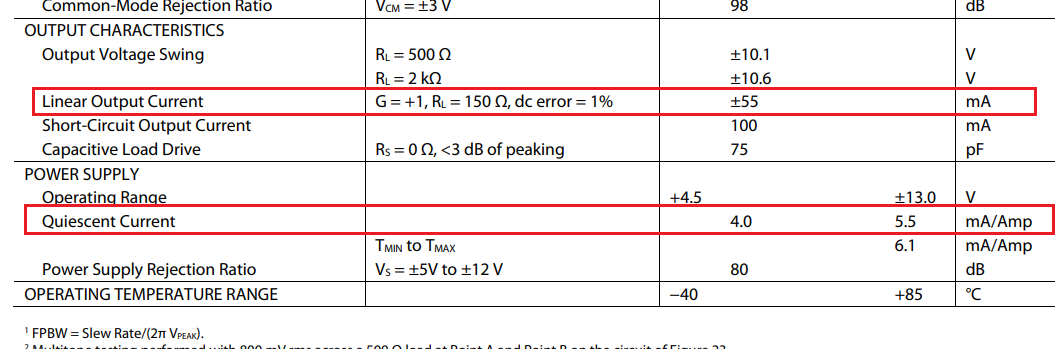

I am trying to do paper calculation for current requirement for OPAMP AD8022

I would like to make sure how much current required by OPAMP when it is in operation mode.

I have captured below snapshot from PAGE No: 3

I have supply voltage: +-5V

So 55 mA is the correct current which will draw from my power supply? or 55mA+11mA=66mA (Quicent current of both opamp) or something else?

I

I am trying to do paper calculation for current requirement for OPAMP AD8022

I would like to make sure how much current required by OPAMP when it is in operation mode.

I have captured below snapshot from PAGE No: 3

I have supply voltage: +-5V

So 55 mA is the correct current which will draw from my power supply? or 55mA+11mA=66mA (Quicent current of both opamp) or something else?

I