Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

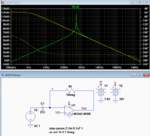

The resistor provides DC negative feedback with a DC gain of 1.Can any one help me in the Figure bellow,

1. Why are there capacitor (0.1u) and resistor (10M) in the circuit of the open loop response?

2. what the reason of there capacitor and resistor ?

The circuit is called an op amp open-loop gain test circuit.3.what is the called this circuit?

4. and why the non-inverting feeding VDD/2?

Good catch.The test circuit is flawed respectively isn't suited to measure the open loop frequency response. To achieve the plotted frequency response, the capacitor must have a factor 1e6 higher value.

Hi,

I´m not sure bout this.

The capacitor and the feedback resistor forms a differentiator circuit. (not a high pass filter with a -3dB corner frequency)

It has low gain with low frequencies and high gain at high frequencies.

This may be used to compensate for the first order low pass filter characteristic of the OPAMP.

The benefit is that the output voltage dynamic is not that big as without the differentiator circuit. During the whole bandwidth of the first order section the output voltage should be constant.

But indeed the circuit is not useful to measure DC gain. Additionally this is feedbacked circuit and not an open loop circuit.

As said: I´m not sure.

Klaus