mpig09

Full Member level 4

- Joined

- Aug 26, 2005

- Messages

- 232

- Helped

- 8

- Reputation

- 16

- Reaction score

- 2

- Trophy points

- 1,298

- Location

- Taipei

- Activity points

- 2,810

Hi all:

There are two nmos models in the spice model : isolation nmos and normal nmos.

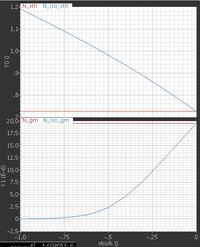

I simulate the i-v curve, and the result shows the curve are the same with isolation nmos and normal nmos.

Does anyone know the difference of application and layout between isolation nmos and normal nmos ?

Thanks for your view and reply.

mpig

There are two nmos models in the spice model : isolation nmos and normal nmos.

I simulate the i-v curve, and the result shows the curve are the same with isolation nmos and normal nmos.

Does anyone know the difference of application and layout between isolation nmos and normal nmos ?

Thanks for your view and reply.

mpig