KingMoshe

Member level 2

Hi all,

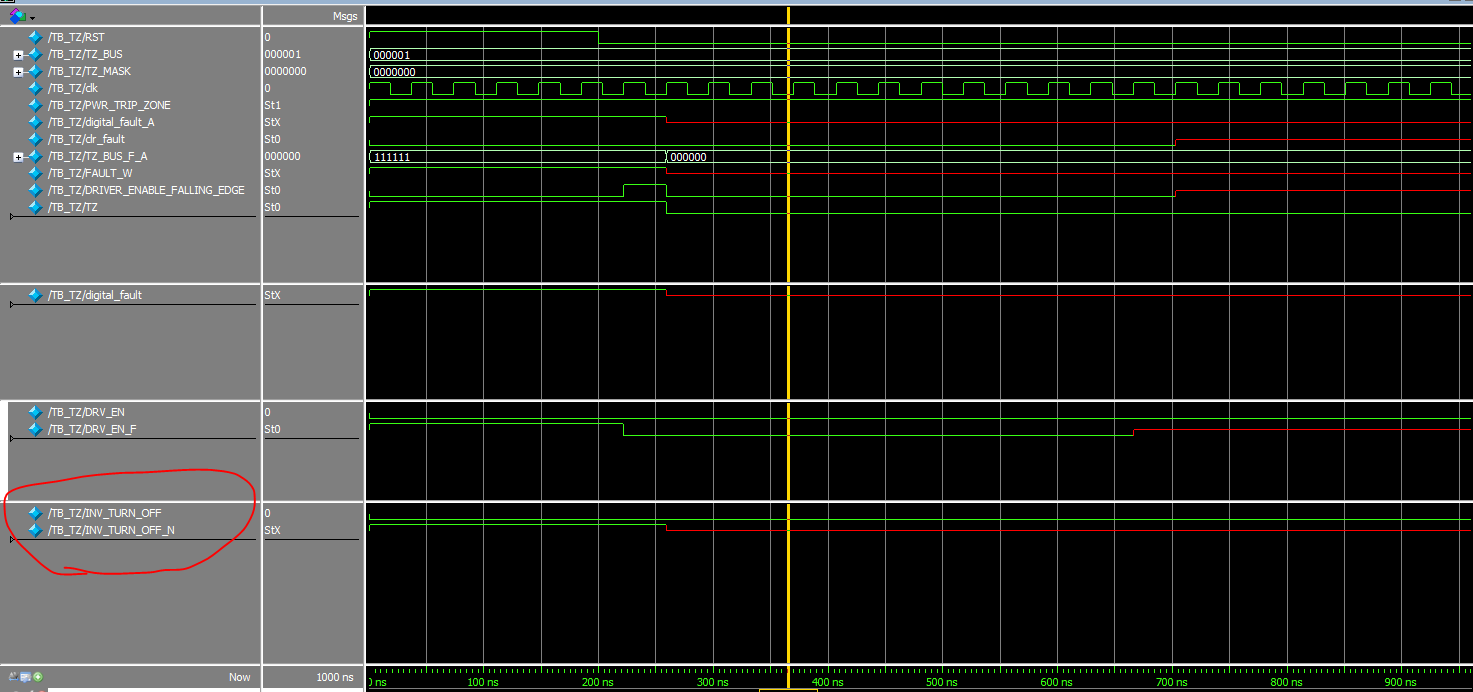

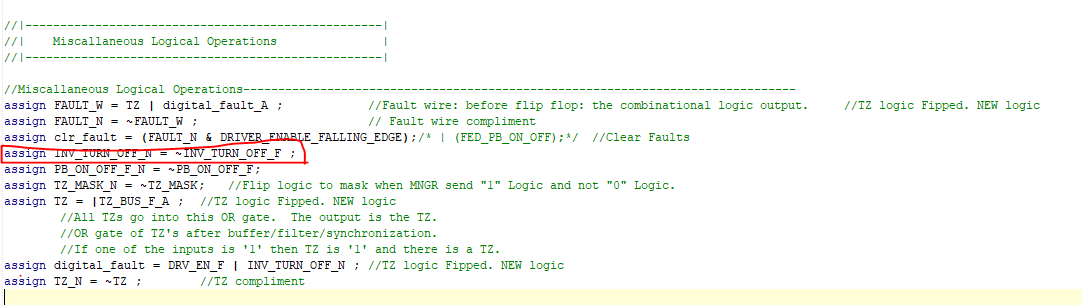

I made a testbench to test my module and I see weird behavior.

please look at the signal INV_TURN_OFF and INV_TURN_OFF_N.

The relation between the two signals is: INV_TURN_OFF_N = ~INV_TURN_OFF.

I don't understand why the signal INV_TURN_OFF_N got value StX.

I made a testbench to test my module and I see weird behavior.

please look at the signal INV_TURN_OFF and INV_TURN_OFF_N.

The relation between the two signals is: INV_TURN_OFF_N = ~INV_TURN_OFF.

I don't understand why the signal INV_TURN_OFF_N got value StX.