electronics_rama

Member level 3

Hi All,

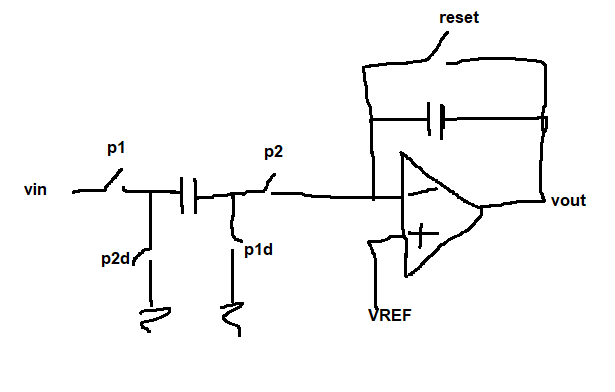

I am simulating the below-switched cap integrator circuit configuration. I have used the verilog-A model for the amplifier. Whenever I set VREF as 0V, I see the vout integrating the output properly. If I set the VREF anything other than 0V, I see VOUT as not an integrated value of the input. What is that I am missing here? Can anybody help?

Thanks,

Rama

I am simulating the below-switched cap integrator circuit configuration. I have used the verilog-A model for the amplifier. Whenever I set VREF as 0V, I see the vout integrating the output properly. If I set the VREF anything other than 0V, I see VOUT as not an integrated value of the input. What is that I am missing here? Can anybody help?

Thanks,

Rama