barbs2021

Newbie level 5

Good day,

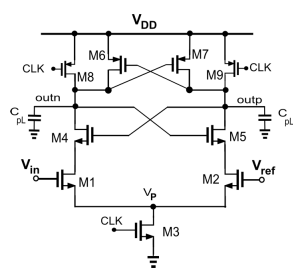

I am trying to simulate a strongARM comparator. As shown below, the inputs are indicated as Vin and Vref. In my testbench, I used vsource with a dc voltage of 1.8V for Vref and 1.8V sine wave (vsource) set at a frequency of 10 MHz for initial testing. Simulation is done using 180nm CMOS technology in SYNOPSYS Custom Designer Tool. Is this the right thing to do? I need corrections and suggestions. Hoping for kind and constructive response.

I am trying to simulate a strongARM comparator. As shown below, the inputs are indicated as Vin and Vref. In my testbench, I used vsource with a dc voltage of 1.8V for Vref and 1.8V sine wave (vsource) set at a frequency of 10 MHz for initial testing. Simulation is done using 180nm CMOS technology in SYNOPSYS Custom Designer Tool. Is this the right thing to do? I need corrections and suggestions. Hoping for kind and constructive response.