claudio_gratton

Newbie

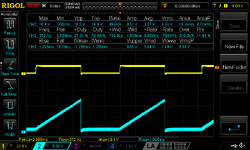

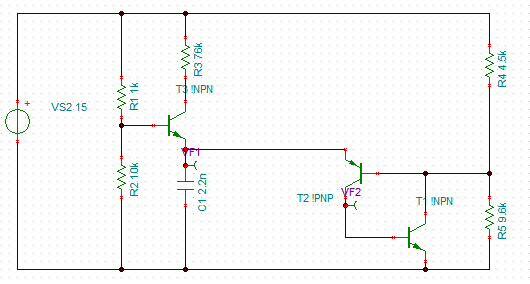

I built this 500Hz, 0-10V sawtooth wave generator i found online. I get the first block, which is just a constant current generator. But i've never seen such a transistor configuration, found in the second block. I guess it turns on the PNP when the capacitor gets to 10V, which turns on the NPN which keeps the PNP on until the capacitor reaches 0V. I'd like an explanation and some formulas, thanks

]

]