engr_joni_ee

Advanced Member level 3

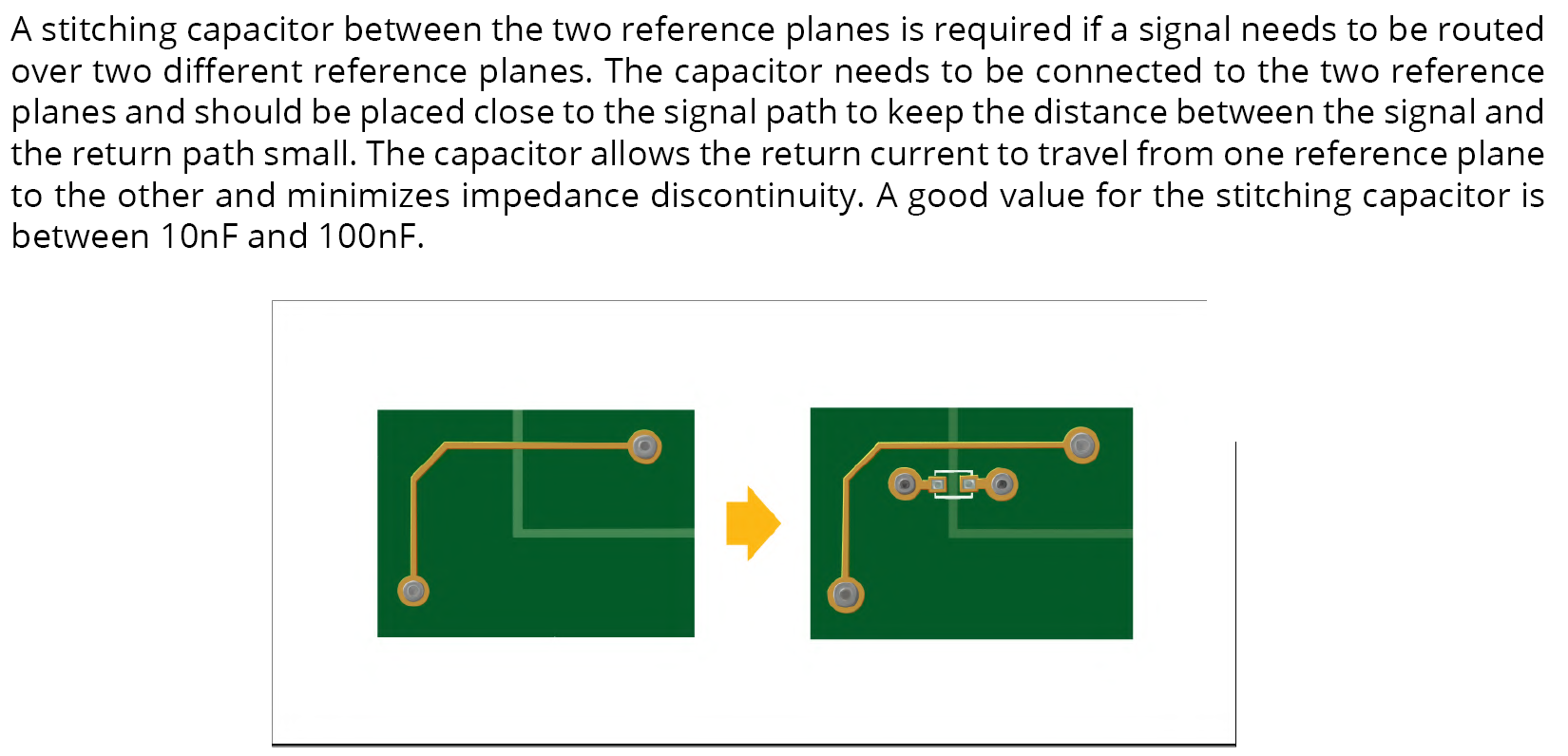

I have found some text regarding stitching via. I am wondering how about if the two reference planes are power planes with different voltages on them. Can we also put stitching via using capacitor between them if a high speed signal is routed over the split ? How about if we have 1.8 V and 3.3 V as reference power planes for high speed signal ?

Can this be two ground planes ? for example analog ground plane and digital ground plane ?

In case they are power and ground plane then it's fine to use decoupling capacitors. But how about if both of them are power planes or both of them are ground planes ? Can we use capacitors to stitch them ?

Can this be two ground planes ? for example analog ground plane and digital ground plane ?

In case they are power and ground plane then it's fine to use decoupling capacitors. But how about if both of them are power planes or both of them are ground planes ? Can we use capacitors to stitch them ?