yefj

Advanced Member level 4

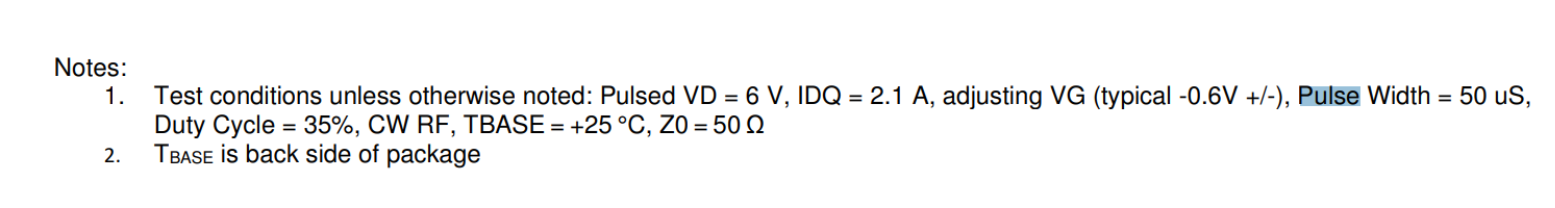

Hello,I need to deliver about 3A and 6V in a pulse as shown bellow from the datasheet threw a VIA.

the problem is thickness of the VIA hole is 18um.

i thought of putting several via's in parralel to supply such current but i am afraid of signal integrity issues.

Could you please recomend me a common Via strategy for delivering such high current to the amplifier?

inner hole plating thickness is 18um its extremely thin.

The not practical solution is to make 5 or 6 such VIAS in paralel.

but i need to know how much current can wistand such via.

putting VIAS in parralell will make their total inductance smaller because inductors in parralell which is good for signal integrity.

maybe i could try to ask the manufacturer if the inner plating could be thicker.

It would be great if you could recommend me some reading material on the subject.

Thanks.

https://www.qorvo.com/products/p/QPA2575

the problem is thickness of the VIA hole is 18um.

i thought of putting several via's in parralel to supply such current but i am afraid of signal integrity issues.

Could you please recomend me a common Via strategy for delivering such high current to the amplifier?

inner hole plating thickness is 18um its extremely thin.

The not practical solution is to make 5 or 6 such VIAS in paralel.

but i need to know how much current can wistand such via.

putting VIAS in parralell will make their total inductance smaller because inductors in parralell which is good for signal integrity.

maybe i could try to ask the manufacturer if the inner plating could be thicker.

It would be great if you could recommend me some reading material on the subject.

Thanks.

https://www.qorvo.com/products/p/QPA2575