cczhangpjzj

Newbie level 4

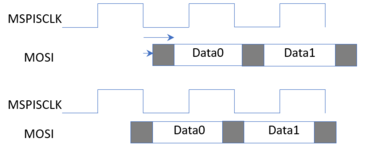

For SPI mode 0, functional operation is always data transmitted at SCK falling edge, then data is to be sampled at SCK rising edge.

But if you were to refer to https://www.ftdichip.com/Support/Documents/DataSheets/ICs/DS_FT800.pdf Figure 6-1 with Tod, the input to SPI slave is sampled at SCK rising edge. SPI slave output then seems it can be sampled at SCK falling or rising at the SPI master side.

And if you refer to https://datasheet.lcsc.com/lcsc/2101051104_Goodix-Technology-GR5515IGND_C2680494.pdf Figure 10-21 with tHMO/tHMO, this is similar that the data seems can be safely sampled at both SPIM SCK rising and falling edge.

Especially when SPIM SCK freq is high, then at SPIM side using SCK falling edge to sample input data can relax the setup time for SPIS output to SPIM input path. Is my understanding correct? And is people doing this way?

But if you were to refer to https://www.ftdichip.com/Support/Documents/DataSheets/ICs/DS_FT800.pdf Figure 6-1 with Tod, the input to SPI slave is sampled at SCK rising edge. SPI slave output then seems it can be sampled at SCK falling or rising at the SPI master side.

And if you refer to https://datasheet.lcsc.com/lcsc/2101051104_Goodix-Technology-GR5515IGND_C2680494.pdf Figure 10-21 with tHMO/tHMO, this is similar that the data seems can be safely sampled at both SPIM SCK rising and falling edge.

Especially when SPIM SCK freq is high, then at SPIM side using SCK falling edge to sample input data can relax the setup time for SPIS output to SPIM input path. Is my understanding correct? And is people doing this way?