yefj

Advanced Member level 4

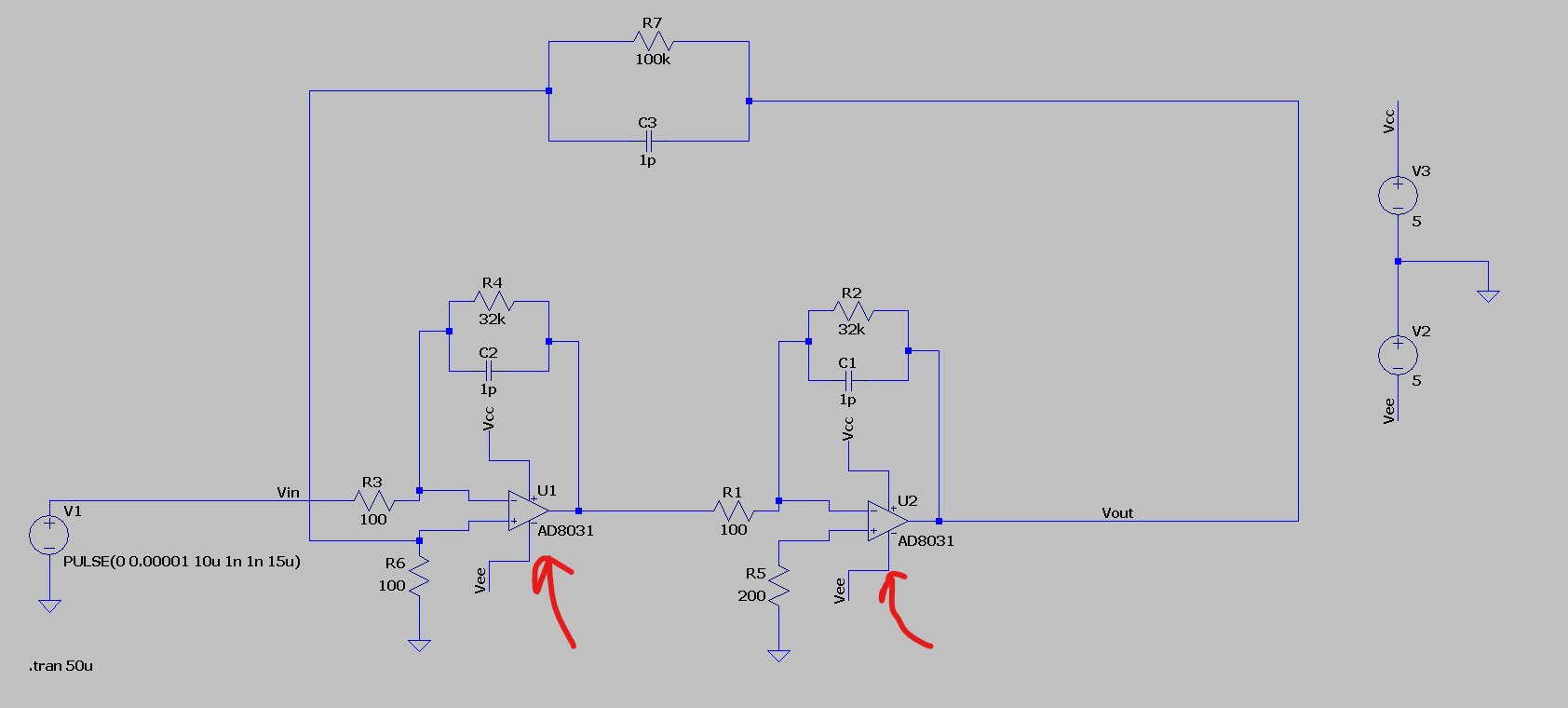

Hell i have a single 5V DC power sourse for two opamps.

the problem is we both opamps open we have a double load so if i connect in parralel my power suplly then my current will be half for each opamp.

given the data sheet bellow,each opamp needs 80uA current,so i put 160uA on my power suply

How do i know the minimal trace width/tickness i need it could sustain this 160uA current threw it?

Thanks.

the problem is we both opamps open we have a double load so if i connect in parralel my power suplly then my current will be half for each opamp.

given the data sheet bellow,each opamp needs 80uA current,so i put 160uA on my power suply

How do i know the minimal trace width/tickness i need it could sustain this 160uA current threw it?

Thanks.