dimBulb

Newbie level 2

Hello,

I'm looking to switch a 10~30V load at up to 5A from a 3.3V microcontroller.

Driving a low side logic level N-Channel Mosfet directly from the 3.3V functions but the mosfet burns out if the switching speed gets much faster than 5K, lack of voltage and charge current. I'd like to acheive on/off speeds around 100-200ns.

I've considered a few options and would really like to know what the common approach is for this sort of situation.

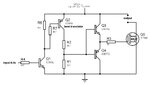

1) Change to High-Side P-Channel and use a transistor to bring the gate towards ground. Gives me a bit higher RDS and I need additional measures to try and keep the gate from exceeding -20V when the supply is 20V+. Zener clipping circuit perhaps?

2) Intelligent Power Switches - would be fantastic but don't have the desired switching speeds, and costs do seem a bit high.

3) Use a mosfet driver. Most have a vcc limit below my supply limit and I'm hoping not to have to run another supply level. Application has potential for 100% on time so bootstrapping wouldn't work.

Throwing on another regulator and using a driver may be the easiest option.

Is there another alternative I'm not considering?

Is running a gate level supply common place in this sort of design?

High-side / low-side / N-Channel / P-Channel, I'm not really stuck on any of them, I'd like to keep the costs and component count down though.

Thanks In Advance.

I'm looking to switch a 10~30V load at up to 5A from a 3.3V microcontroller.

Driving a low side logic level N-Channel Mosfet directly from the 3.3V functions but the mosfet burns out if the switching speed gets much faster than 5K, lack of voltage and charge current. I'd like to acheive on/off speeds around 100-200ns.

I've considered a few options and would really like to know what the common approach is for this sort of situation.

1) Change to High-Side P-Channel and use a transistor to bring the gate towards ground. Gives me a bit higher RDS and I need additional measures to try and keep the gate from exceeding -20V when the supply is 20V+. Zener clipping circuit perhaps?

2) Intelligent Power Switches - would be fantastic but don't have the desired switching speeds, and costs do seem a bit high.

3) Use a mosfet driver. Most have a vcc limit below my supply limit and I'm hoping not to have to run another supply level. Application has potential for 100% on time so bootstrapping wouldn't work.

Throwing on another regulator and using a driver may be the easiest option.

Is there another alternative I'm not considering?

Is running a gate level supply common place in this sort of design?

High-side / low-side / N-Channel / P-Channel, I'm not really stuck on any of them, I'd like to keep the costs and component count down though.

Thanks In Advance.