hoka_89

Newbie level 4

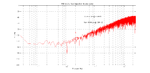

i am working on a sigma delta adc second order three bit and i do the schematic design on cadence and i get 100 db and it is ok when i make the layout and make post layout it become 93db i found in the drawing of fft a pulse at another frequency 200hz(my input frequency is 100hz and band width is 200)

and this is the picture

and this is the picture