bharat_tangudu

Member level 1

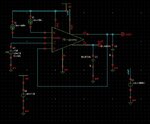

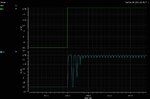

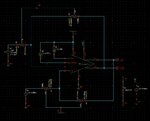

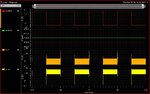

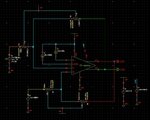

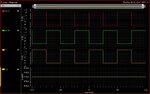

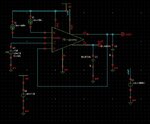

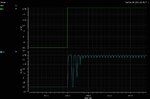

I have designed two-stage fully differential opamp. I took the results and seems every parameter is giving good results except settling time (I believe). To check this, I connected in unity gain configuration and applied the pulse input of 500us (probably, I may be wrong in circuit setup). output is not settling when i run the circuit. Can someone suggest me what to do if settling time has gone worst.

If settling time is not the parameter because of which opamp is giving improper results, can somebody clarify me which one is causing the distortion in output.

Gain 89.5531dB

3dB frequency 903.82Hz

Phase Margin 72.29degrees

Unity Gain bandwidth 45.19MHz

Current in output branch 40.47uA

Bias current 20uA

I am attaching the setup for unity gain amplifier, output

If settling time is not the parameter because of which opamp is giving improper results, can somebody clarify me which one is causing the distortion in output.

Gain 89.5531dB

3dB frequency 903.82Hz

Phase Margin 72.29degrees

Unity Gain bandwidth 45.19MHz

Current in output branch 40.47uA

Bias current 20uA

I am attaching the setup for unity gain amplifier, output