Saransh22

Newbie level 5

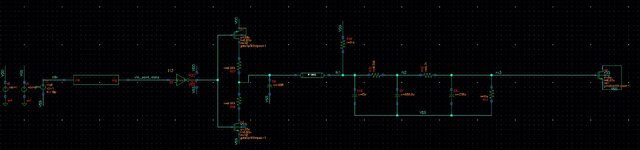

What will be the suitable frequency range for SENT interface, for 0.03u technology in cadence?

Please explain what can prove that this is the good frequency for my receiver circuit?

In a paper two frequencies are mentioned one is 125KHz clock and other 625Mhz which should be used while simulating in cadence?

Thankyou.

Please explain what can prove that this is the good frequency for my receiver circuit?

In a paper two frequencies are mentioned one is 125KHz clock and other 625Mhz which should be used while simulating in cadence?

Thankyou.