Milestone

Newbie level 3

- Joined

- May 17, 2009

- Messages

- 3

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,306

Hello,

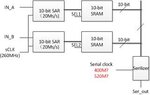

I am designing a 10-bit SAR ADC and it's output chain. My SAR ADC input is 20MHz(mCLK), internally with PLL multiply to 260MHz(sCLK), with 3 sCLK to finish T/H, and 10 sCLK for conversion. Is it possible for me to use a 200MHz clock to serial output the 10-bit digital data.

I think the syncronization is a big problem for me. Or I need to use the available 260MHz clock to output my data(output 10-bit digital data and then insert another dummy data).

Best,

Cheng

I am designing a 10-bit SAR ADC and it's output chain. My SAR ADC input is 20MHz(mCLK), internally with PLL multiply to 260MHz(sCLK), with 3 sCLK to finish T/H, and 10 sCLK for conversion. Is it possible for me to use a 200MHz clock to serial output the 10-bit digital data.

I think the syncronization is a big problem for me. Or I need to use the available 260MHz clock to output my data(output 10-bit digital data and then insert another dummy data).

Best,

Cheng