syee10

Member level 3

Hi,

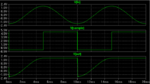

Anyone here can tell me how to connect a Sample and Hold IC LF398 in practical so that i can get a V(out) waveform as shown in the attached file? The V(in) and V(sample) is shown in the attached file also. Please provide me a simple schematic diagram if possible. The datasheet can be found in the following links:

LF398 pdf, LF398 description, LF398 datasheets, LF398 view ::: ALLDATASHEET :::

Anyone here can tell me how to connect a Sample and Hold IC LF398 in practical so that i can get a V(out) waveform as shown in the attached file? The V(in) and V(sample) is shown in the attached file also. Please provide me a simple schematic diagram if possible. The datasheet can be found in the following links:

LF398 pdf, LF398 description, LF398 datasheets, LF398 view ::: ALLDATASHEET :::