davison7

Junior Member level 2

- Joined

- Aug 30, 2008

- Messages

- 22

- Helped

- 2

- Reputation

- 4

- Reaction score

- 1

- Trophy points

- 1,281

- Activity points

- 1,456

Hi~~Everybody,

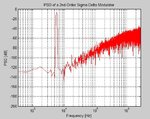

Recently, I have designed a second-order Sigma-delta modulator using the CIFB architecture.

The fin = 1KHz, fs = 1MHz, and Vin = 1V.

In the first, I use the Matlab to simulate its function. The output spectrum shows that the noise floor at dc frequency is about -120dB.

But when I use the actual devices of the OPA, the Switch, and the clock generator into the Spectre for simulation, the low-frequency noise floor

rises at -90dB. It results in a worse SNR!

Could eveyone tells me that what reasons cause the low-frequency noise floor becomes worse and how to improve this problem?

Thank you very much

Recently, I have designed a second-order Sigma-delta modulator using the CIFB architecture.

The fin = 1KHz, fs = 1MHz, and Vin = 1V.

In the first, I use the Matlab to simulate its function. The output spectrum shows that the noise floor at dc frequency is about -120dB.

But when I use the actual devices of the OPA, the Switch, and the clock generator into the Spectre for simulation, the low-frequency noise floor

rises at -90dB. It results in a worse SNR!

Could eveyone tells me that what reasons cause the low-frequency noise floor becomes worse and how to improve this problem?

Thank you very much