ronptihi

Newbie

hi

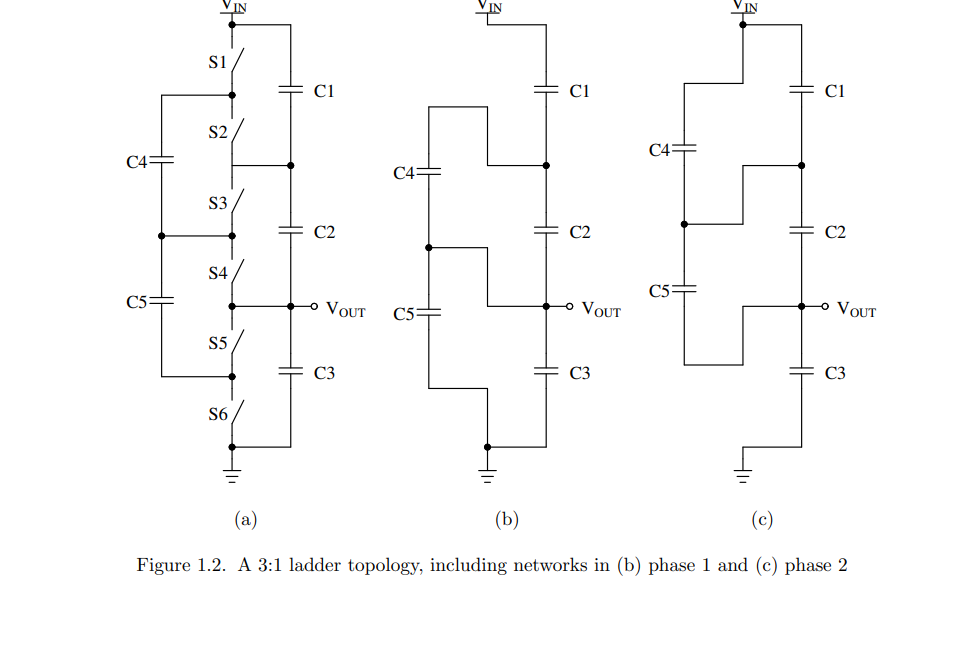

i wanted to build this circuit to try to understand him , from what i know in phase 1: vout=0.25 vin , and phase 2 :vout= 0.5 vin.

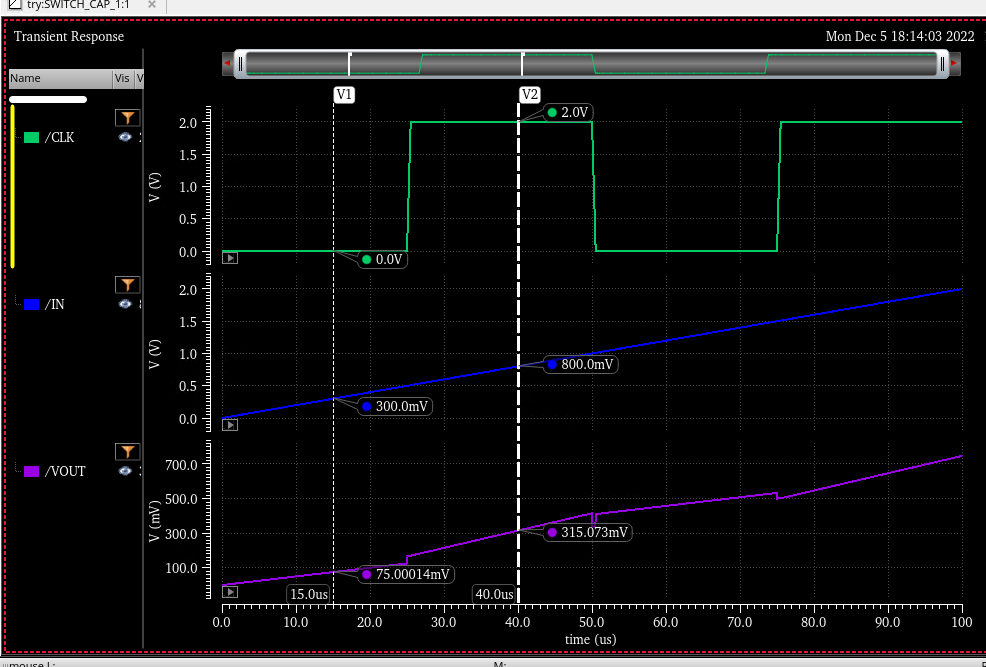

so i run transient simulation to see that my theory correct

and i see in phase 1 when clk is 0 that vout is 0..25 vin

but in phase 2 when clk is VDD, vout is not 0.5 vin actually vout is 0.39 vin

why this is happen ?

i wanted to build this circuit to try to understand him , from what i know in phase 1: vout=0.25 vin , and phase 2 :vout= 0.5 vin.

so i run transient simulation to see that my theory correct

and i see in phase 1 when clk is 0 that vout is 0..25 vin

but in phase 2 when clk is VDD, vout is not 0.5 vin actually vout is 0.39 vin

why this is happen ?