stoned

Member level 3

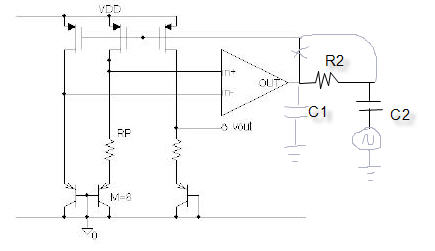

1/f noise and bandgap

Hi all:

The PM of the whole loop should be considered carefully to avoid oscillations.

So I want to confirm it and get PM of the whole loop of my circuit by simulating. The figure as the following.

I break the loop at the Opamp output node, and add AC source series a capacitance at the gate of the top PMOS, and plot the Amp out node result. But the result is about -20dB of opamp output node. It’s right?

Can somebody give me the detail method of simulation to get PM?

Large signal stability:

I calculated the positive and negative feedback respectively, finding that positive is large than the negative, but the sum is small than unit.

When I ramp the Vdd from 0 to Vdd during 1ns, the BandGap will be stable after 3us, and with some ring during these time, so I think the phase margin is not enough, how to solve this problem? Add capacitance between out and ground?

Noise:

Does noise simulation required the noise model? When I use the following cmd to simulate.

vdd vdda 0 vol ac=1

.ac dec 10 .1 10

.noise v(vref) vdd

.print noise inoise

the result is

**** the results of the sqrt of integral (v**2 / freq)

**** total output noise voltage = 63.5984u volts

**** total equivalent input noise = 200.0866m volts

******

how to simulate the noise?

Thanks a lot!

stoned

Hi all:

The PM of the whole loop should be considered carefully to avoid oscillations.

So I want to confirm it and get PM of the whole loop of my circuit by simulating. The figure as the following.

I break the loop at the Opamp output node, and add AC source series a capacitance at the gate of the top PMOS, and plot the Amp out node result. But the result is about -20dB of opamp output node. It’s right?

Can somebody give me the detail method of simulation to get PM?

Large signal stability:

I calculated the positive and negative feedback respectively, finding that positive is large than the negative, but the sum is small than unit.

When I ramp the Vdd from 0 to Vdd during 1ns, the BandGap will be stable after 3us, and with some ring during these time, so I think the phase margin is not enough, how to solve this problem? Add capacitance between out and ground?

Noise:

Does noise simulation required the noise model? When I use the following cmd to simulate.

vdd vdda 0 vol ac=1

.ac dec 10 .1 10

.noise v(vref) vdd

.print noise inoise

the result is

**** the results of the sqrt of integral (v**2 / freq)

**** total output noise voltage = 63.5984u volts

**** total equivalent input noise = 200.0866m volts

******

how to simulate the noise?

Thanks a lot!

stoned