jasonxilion

Junior Member level 1

hello all

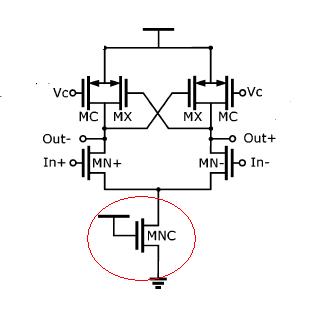

recently i am dealing with a vco, i paste it on the web, can u see?

it is a delay cell, vc is the contral voltage of the vco. i think most of u are familiar with this kind of vco.

my QUESTION is : why the gate of MNC be connected to vdd, to operate in triode region?

a paper says that it allows the full amplitude of oscillated signal within a wide range. but i don't know why. anyone can tell me why?

and more, what the effect of the MNC to the phase noise of vco?

recently i am dealing with a vco, i paste it on the web, can u see?

it is a delay cell, vc is the contral voltage of the vco. i think most of u are familiar with this kind of vco.

my QUESTION is : why the gate of MNC be connected to vdd, to operate in triode region?

a paper says that it allows the full amplitude of oscillated signal within a wide range. but i don't know why. anyone can tell me why?

and more, what the effect of the MNC to the phase noise of vco?