tarjina

Junior Member level 3

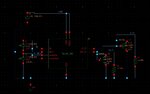

Hello everyone. I am simulating a very easy circuit with CMOS. It has two pMOS power switches. Each connected to two inverters in series. The circuit looks like below:

So, when the Enable is low, the output should follow input and when enable is high, we are cutting off the power so the output should be low (I need low, not the previous state).

so I need a pull down network. But, the problem is I cannot connect a resistor to the vdd_internal. Because, we can not touch the layout.

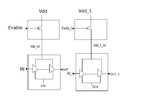

Now, I have created a test bench to test this circuit. It looks like below:

now, how can I insert the pull down network in this testbench? or any other ideas to pull down the vdd_internal to 0 when the power supply is OFF?

Thanks in advance.

So, when the Enable is low, the output should follow input and when enable is high, we are cutting off the power so the output should be low (I need low, not the previous state).

so I need a pull down network. But, the problem is I cannot connect a resistor to the vdd_internal. Because, we can not touch the layout.

Now, I have created a test bench to test this circuit. It looks like below:

now, how can I insert the pull down network in this testbench? or any other ideas to pull down the vdd_internal to 0 when the power supply is OFF?

Thanks in advance.