Kerrowman

Member level 4

- Joined

- Oct 12, 2021

- Messages

- 75

- Helped

- 0

- Reputation

- 0

- Reaction score

- 2

- Trophy points

- 8

- Location

- West Penwith

- Activity points

- 578

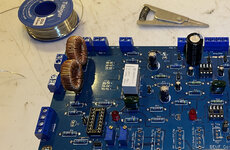

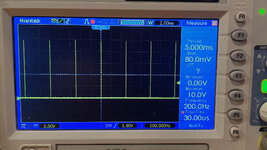

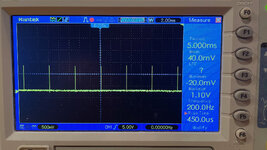

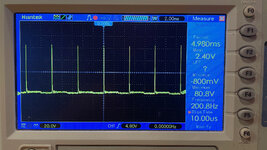

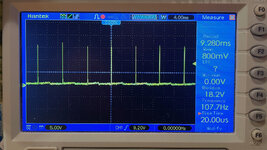

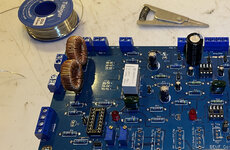

In my doing some research into the effects of HV CEMF pulses on batteries, I am finding that my MOSFETs understandably get easily damaged by these pulses, even when I have tried to isolate and protect them using a pair of chokes (see pic).

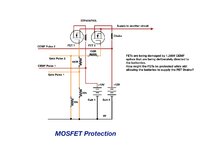

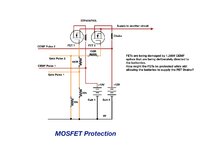

I also attach the relevant part of the circuit and wondered if anyone had any straightforward ideas as to how to block the CEMF pulses (~ 1,200V) from reaching the FETs? Maybe a fast diode between the Drain and Source of each one? However, the Source does not connect to Ground but supplies another part of the circuit.

Thanks

I also attach the relevant part of the circuit and wondered if anyone had any straightforward ideas as to how to block the CEMF pulses (~ 1,200V) from reaching the FETs? Maybe a fast diode between the Drain and Source of each one? However, the Source does not connect to Ground but supplies another part of the circuit.

Thanks