David_

Advanced Member level 2

I haven't actually tested this i real world circuit, I was about to order the MOSFET when I realized that some thing was wrong. So far it is all LTspice, is it possible that this is a LTspice fluke?

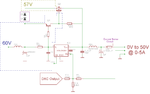

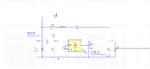

In any case here is the circuit:

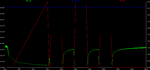

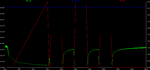

What will follow here is first a plot of the input and output voltage and load current but the green trace is a collection of 76 steps, the upper resistor in the regulator feedback voltage divider is 1meg in the plot while the lower resistor starts at 25k and in 76 steps goes up to 400k.

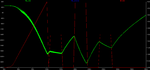

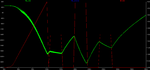

The second plot is just the same only I have flipped drain and source of the FET:

I am in the process of designing a neat PCB to test this setup in reality while fixing a few things that was not good in the last prototype, and I intend to prove that your(Klaus) hypothetical regulator control circuit can indeed go down to 0V or just about.

Regards

In any case here is the circuit:

What will follow here is first a plot of the input and output voltage and load current but the green trace is a collection of 76 steps, the upper resistor in the regulator feedback voltage divider is 1meg in the plot while the lower resistor starts at 25k and in 76 steps goes up to 400k.

The second plot is just the same only I have flipped drain and source of the FET:

I am in the process of designing a neat PCB to test this setup in reality while fixing a few things that was not good in the last prototype, and I intend to prove that your(Klaus) hypothetical regulator control circuit can indeed go down to 0V or just about.

Regards