powerelectronics_beginner

Newbie level 6

Hi guys, we designed a PCB with the formerly mentioned CREE Six-Pack module and 3 pcs. of Si8233 Gate Drivers, one for each phase leg to work as a pure sine wave 50Hz AC inverter. We configured the µC to drive 2 legs in full bridge configuration with filtering inductance and capacitor as well as load resistor between two legs with inverted modulation so that FET 1 and 4 are conducting simultaneously followed by 2 and 3. Software is working fine, we have no control circuit and current measurement in there yet and driving it with the help of a look-up table - 50Hz sine with peak value according to the set DC-link voltage appears on the output clamps correctly.

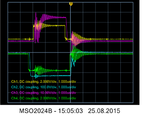

Now lets get to the problem. Our minimum load is approximately 80Ohms. With this load we are able to increase the DC-link voltage up to 130V, than the 50Hz sine is getting bad caused by faulty gate signals, it starts to break in near its amplitude. The PWM coming from the TI µC board is getting bad as well and starts to oscillate getting below the lower threshold of 0.8V which causes the Si8233 gate signal malfunction. When we decrease the load resistance to 60Ohms this problem is starting earlier at 70V dc-link voltage.

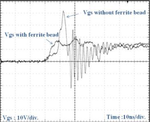

Now we disconnected the coil so that every phase-leg can work without any load and on its own, when DC-link voltage is 0V everything is fine, gate signals are ok. But when we turn up the dc-link voltage and the switching nodes have different voltage levels the problem starts to occur and the PWM signal starts to oscillate even with no load current flowing through the FETs because of the open load circuit. We checked dead-time, gate resistors (tested with 10R,20R,40R) and we soldered ferrite beads to the gate pins like it is recommended by CREE in their circuit for the SIC evaluation board with SI8233 driver as well. We also pull the gate to -5V by using zener diodes for faster turn of like it seems to be common design practice considering example circuits from different manufacturers. The 24V isolated supply voltage for the driver gets supplied by RECOM R2S-0524 isolated DC-DC converters soldered near the drivers which provide us the isolated voltages and grounds for the 6 different gate circuits.

Do you guys have any idea how the gate driver can cause the PWM signal to oscillate? We think that this shouldnt be possible in any way. We also soldered the PWM signal leads directly and as short as possible to the PWM input pins 1 and 2 of the gate driver to mend the potential problem of the long PWM traces inside the PCB.

Maybe someone of you guys can give us a hint on the possible reason for our problem.

Best regards

- - - Updated - - -

this is basically our circuit

this is basically our circuit

Now lets get to the problem. Our minimum load is approximately 80Ohms. With this load we are able to increase the DC-link voltage up to 130V, than the 50Hz sine is getting bad caused by faulty gate signals, it starts to break in near its amplitude. The PWM coming from the TI µC board is getting bad as well and starts to oscillate getting below the lower threshold of 0.8V which causes the Si8233 gate signal malfunction. When we decrease the load resistance to 60Ohms this problem is starting earlier at 70V dc-link voltage.

Now we disconnected the coil so that every phase-leg can work without any load and on its own, when DC-link voltage is 0V everything is fine, gate signals are ok. But when we turn up the dc-link voltage and the switching nodes have different voltage levels the problem starts to occur and the PWM signal starts to oscillate even with no load current flowing through the FETs because of the open load circuit. We checked dead-time, gate resistors (tested with 10R,20R,40R) and we soldered ferrite beads to the gate pins like it is recommended by CREE in their circuit for the SIC evaluation board with SI8233 driver as well. We also pull the gate to -5V by using zener diodes for faster turn of like it seems to be common design practice considering example circuits from different manufacturers. The 24V isolated supply voltage for the driver gets supplied by RECOM R2S-0524 isolated DC-DC converters soldered near the drivers which provide us the isolated voltages and grounds for the 6 different gate circuits.

Do you guys have any idea how the gate driver can cause the PWM signal to oscillate? We think that this shouldnt be possible in any way. We also soldered the PWM signal leads directly and as short as possible to the PWM input pins 1 and 2 of the gate driver to mend the potential problem of the long PWM traces inside the PCB.

Maybe someone of you guys can give us a hint on the possible reason for our problem.

Best regards

- - - Updated - - -

this is basically our circuit

this is basically our circuit