afujian

Member level 4

- Joined

- Mar 26, 2010

- Messages

- 70

- Helped

- 2

- Reputation

- 4

- Reaction score

- 1

- Trophy points

- 1,288

- Location

- china

- Activity points

- 1,715

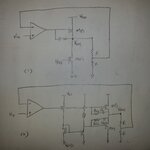

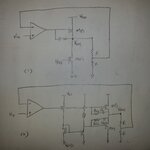

Hi all,I'm designing a output buffer for DAC, and intend to use a 2 stage miller compensated OP or a OP with class-AB output stage as showed in the picture(1) and (2),they are both feedback connected by 2 equal resistors to get a X2 gain,but the simulation show that when the input voltage changes from 0 to 1mV,the output node Vout changes very slow while the target settling time is about 2uS,when the input changes from 1V-1.001V,the output changes normally.I think this is because when the voltage of node Vout is very low,the whole loop doesn't work,so is there any way to solve the probelm? Thanks a lot.

Simulation results

Simulation results