raducrv

Member level 1

Hi ,

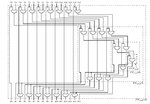

I am trying to make synthesize the circuit in the figure which is a prefix computation network with AND gate . I have done the fallowing code in Verilog but i have some error about the indices

The idea is to use parametrisable recursion

THE CODE:

module PCN #(parameter n = 4)

( output [n-1:0] out ,

input [n-1:0] in );

wire [n/2-1:0] wire0; //wires to PCN(n/2)

wire [n/2-1:0] wire1; //wires from PCN(n/2)

genvar i;

generate

if (n == 2) begin

assign out[0] = in[0];

and and1(out[n-1], in[0], in[n-1]);

end

else

begin

//up ands

for (i=0; i<n/2; i=i+1) begin:up_ands

and and1(wire0, in[i*2], in[i*2+1]);

end

//PCN(n/2) module

PCN #(.n(n/2)) PCN0(.out(wire1),

.in (wire0));

//down ands

for (i=1; i<(n/2-1); i=i+1) begin: down_ands

and and1(out0[i*2+3], in[i*2+2], wire1);

assign zout[i*2+1] = wire1;

end

//first and last input

assign out[0] = in[0];

assign out[n-1] = wire1[n/2-1];

end

endgenerate

endmodule

I am trying to make synthesize the circuit in the figure which is a prefix computation network with AND gate . I have done the fallowing code in Verilog but i have some error about the indices

The idea is to use parametrisable recursion

THE CODE:

module PCN #(parameter n = 4)

( output [n-1:0] out ,

input [n-1:0] in );

wire [n/2-1:0] wire0; //wires to PCN(n/2)

wire [n/2-1:0] wire1; //wires from PCN(n/2)

genvar i;

generate

if (n == 2) begin

assign out[0] = in[0];

and and1(out[n-1], in[0], in[n-1]);

end

else

begin

//up ands

for (i=0; i<n/2; i=i+1) begin:up_ands

and and1(wire0, in[i*2], in[i*2+1]);

end

//PCN(n/2) module

PCN #(.n(n/2)) PCN0(.out(wire1),

.in (wire0));

//down ands

for (i=1; i<(n/2-1); i=i+1) begin: down_ands

and and1(out0[i*2+3], in[i*2+2], wire1);

assign zout[i*2+1] = wire1;

end

//first and last input

assign out[0] = in[0];

assign out[n-1] = wire1[n/2-1];

end

endgenerate

endmodule

Attachments

Last edited: