jebaspaul

Junior Member level 3

- Joined

- Nov 10, 2011

- Messages

- 28

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,283

- Activity points

- 1,499

Hi,

I am designing an 10 Bit 200 MSPS Pipeline ADC in TSMC 65nm process.

Just finished the design of first stage Opamp. It uses the "Folded Cascode Gain Boosted Opamp" architecture. The supply voltage is 3.3V. The total current drawn from the supply is around 90mA. Therefore, the first stage Opamp itself dissipating around 300mW (3.3 * 90mA) of power.

My qns is;

1. Is the power dissipation acceptable. I have achieved 93dB Open loop gain and 1.5GHz of Bandwidth. The bandwidth is higher because it is configured for a closed loop gain of two.

2. if I estimate the total power consumption based on binomial expansion. My design consumes around 300mA of current. So, it dissipates 1W of power(for 10 stages). I have assumed that a stage consumes 70% of current compare to its preceding stage.

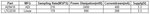

I have done some survey on commercially available Pipeline ADC's for the same spec. I found this;

Thanks,

Jebas.

I am designing an 10 Bit 200 MSPS Pipeline ADC in TSMC 65nm process.

Just finished the design of first stage Opamp. It uses the "Folded Cascode Gain Boosted Opamp" architecture. The supply voltage is 3.3V. The total current drawn from the supply is around 90mA. Therefore, the first stage Opamp itself dissipating around 300mW (3.3 * 90mA) of power.

My qns is;

1. Is the power dissipation acceptable. I have achieved 93dB Open loop gain and 1.5GHz of Bandwidth. The bandwidth is higher because it is configured for a closed loop gain of two.

2. if I estimate the total power consumption based on binomial expansion. My design consumes around 300mA of current. So, it dissipates 1W of power(for 10 stages). I have assumed that a stage consumes 70% of current compare to its preceding stage.

I have done some survey on commercially available Pipeline ADC's for the same spec. I found this;

Thanks,

Jebas.