mohamis288

Full Member level 3

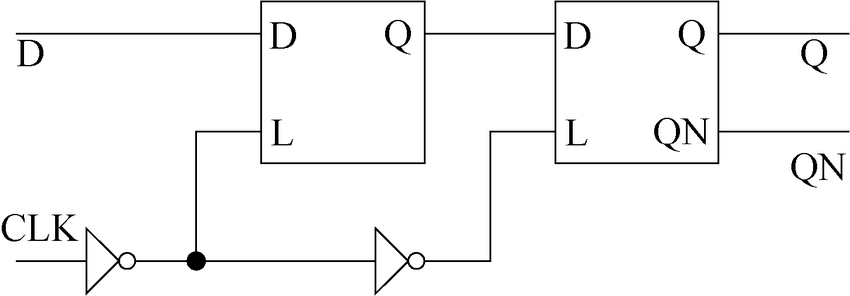

I have implemented the Positive edge-triggered flip flop using the D-latch based diagram in cadence virtuoso.

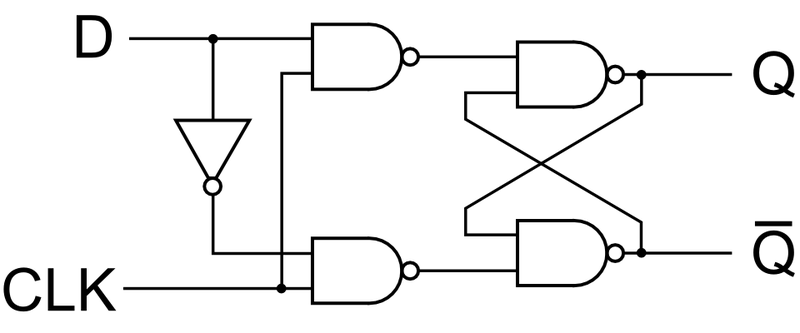

For D-latch I have used the diagram in AckLP.png .

But it seems both edges are working.

What is the reason?

For D-latch I have used the diagram in AckLP.png .

But it seems both edges are working.

What is the reason?