Lucast85

Member level 3

Hi everyone,

I've designed an embedded board with a SOM module based on STM32MP153 microcontroller and a PHY transceiver from ADI, the ADIN1200. The connections between the two devices are the followings (from AN5031 - STM):

I've some issues when I try to communicate with the PHY ADIN 1200.

For example, when I try to read from the read-only register 0x03 (Manufacturer Model nr, etc.), I read different values each time I try to read it. Sometimes the information is correct because I read 0xBC20, other times is very different (e.g. D07F, 9E08, 1000, etc.) and has no-sense.

I thought the PHY is not able to understand the read request received from the MAC of STM32MP1 and it send back the random content of some other registers. However, if I try to ask the content of the register 0x03 of the PHY 0x01, that not exist because the only PHY has address 0x00, no one responds (that is correct). From this experiment it seems that the PHY is able to understand the request from the MAC (at least in the first part, that cointains the PHY address). I thought it could understand also the following part cointainind the register's content.

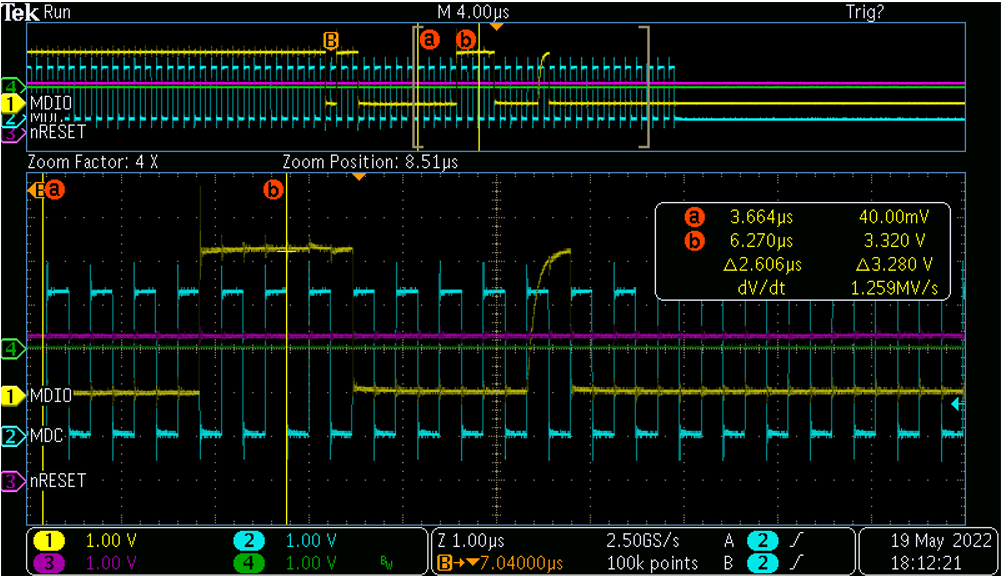

The signals, measured close to the PHY is the following:

From this image,

What could I do to investigate on this issue?

Thank you in advance.

I've designed an embedded board with a SOM module based on STM32MP153 microcontroller and a PHY transceiver from ADI, the ADIN1200. The connections between the two devices are the followings (from AN5031 - STM):

I've some issues when I try to communicate with the PHY ADIN 1200.

For example, when I try to read from the read-only register 0x03 (Manufacturer Model nr, etc.), I read different values each time I try to read it. Sometimes the information is correct because I read 0xBC20, other times is very different (e.g. D07F, 9E08, 1000, etc.) and has no-sense.

I thought the PHY is not able to understand the read request received from the MAC of STM32MP1 and it send back the random content of some other registers. However, if I try to ask the content of the register 0x03 of the PHY 0x01, that not exist because the only PHY has address 0x00, no one responds (that is correct). From this experiment it seems that the PHY is able to understand the request from the MAC (at least in the first part, that cointains the PHY address). I thought it could understand also the following part cointainind the register's content.

The signals, measured close to the PHY is the following:

From this image,

- B marker is at the end of the 32 bit preable;

- b is the marker at the end of the reg. address (0b00011);

- the 1 bit on the MDIO on the right side of the screen is the response from the PHY (that is not obviously 0xBC08);

What could I do to investigate on this issue?

Thank you in advance.