hakim-djz

Junior Member level 2

Hi All,

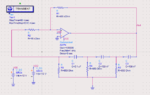

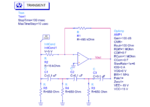

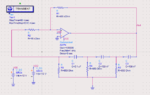

I've been trying to simulate the circuit in the attached image, but not getting the results I want.

The oscillations seem ok, but the magnitude is far off and been going round in circles trying different things.

#In ADS, there's an Ideal OpAmp and standard model; in the schematic attached, I've used the Ideal model, but the example that I'm trying to follow seems to be using the standard model, which I've tried and cannot get the same results. The book that I'm following was published around 2006, so they have been using the older ADS where I think the Ideal wasn't available.

Anyway, if anyone can spot where I'm going wrong or pass any advice would be great.

Thanks in advance,

Hakim

I've been trying to simulate the circuit in the attached image, but not getting the results I want.

The oscillations seem ok, but the magnitude is far off and been going round in circles trying different things.

#In ADS, there's an Ideal OpAmp and standard model; in the schematic attached, I've used the Ideal model, but the example that I'm trying to follow seems to be using the standard model, which I've tried and cannot get the same results. The book that I'm following was published around 2006, so they have been using the older ADS where I think the Ideal wasn't available.

Anyway, if anyone can spot where I'm going wrong or pass any advice would be great.

Thanks in advance,

Hakim