promach

Advanced Member level 4

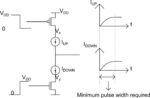

How does the two inverter delay stage in Figure 6.14 on page 265 of Design of CMOS RF Integrated Circuits and Systems helps to eliminate dead zone in Phase Frequency Detector ?

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

The two inverters ensure that the UP and DOWN signals need to be both HIGH for atleast two inverter delays before they are reset to LOW.

The 2 inverters are needed to provide delays for the UP and Down current source to turn on.

We may use more even number inverters stage if needed to ensure the current sources are turn on.

Typically, the delay in turning on a current source > delay of a simple logic gate. It cannot reach metastability.

When the reference and feedback clocks are exactly aligned and you have the reset pulse width exactly equal to the delay in current source turning on, then both the currents reach the final value before being turned off.

I presume there's a certain probability and I don't see how it could be avoided in any of the shown circuits. But why you think that it will affect PFD operation? Did you analyze the output signals in case of metastability?I am still not convinced on why the SR latches will NEVER enter metastable state.

What ? I do not understand this above statement.

Could you rephrase this sentence ?

If the total width of UP or DOWN in such a case has been made equal to the delay in turning on the current source, then both the current sources will reach their final value (the value for which you would have designed your current source), before starting to turn off again.

Therefore, the reset signal edge is far away from REF and FEEDBACK clocks. There is therefore very low probability of metastability.

Look at the two D flip-flop variant of the PFD detector.