engr.waqas

Full Member level 3

- Joined

- Jul 21, 2009

- Messages

- 172

- Helped

- 13

- Reputation

- 26

- Reaction score

- 10

- Trophy points

- 1,298

- Location

- karachi,Pakistan

- Activity points

- 2,342

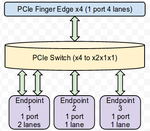

Considering the following scenario:

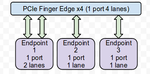

A designer wants to connect 3 devices on a PCIe x4 finger edge connector, commonly found on mother boards. All 3 devices will be populated on the same PCIe card. One device has 1 port of 2 lanes i.e (1 x2 PCIe port) Remaining two devices have 1 port of 1 lane (1 x1 PCIe port) each.

Scheme 1:

Scheme 2:

I've seen scheme 1 in the datasheets of some PCIe switches. I want to know if a PCIe switch is really required in this case.

What if we omit the switch and just split the PCIe lanes?

Will it be a legit PCIe network?

If yes then how will bus numbers be assigned?

Kindly ask if there is a need for clarification.

A designer wants to connect 3 devices on a PCIe x4 finger edge connector, commonly found on mother boards. All 3 devices will be populated on the same PCIe card. One device has 1 port of 2 lanes i.e (1 x2 PCIe port) Remaining two devices have 1 port of 1 lane (1 x1 PCIe port) each.

Scheme 1:

Scheme 2:

I've seen scheme 1 in the datasheets of some PCIe switches. I want to know if a PCIe switch is really required in this case.

What if we omit the switch and just split the PCIe lanes?

Will it be a legit PCIe network?

If yes then how will bus numbers be assigned?

Kindly ask if there is a need for clarification.