engr_joni_ee

Advanced Member level 3

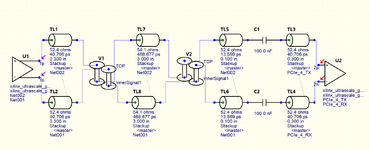

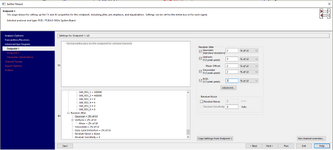

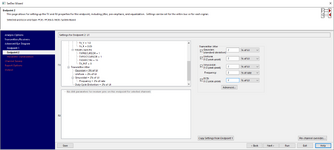

I am running pre-layout simulation in LineSim in HyperLynx. I have attached the pre-layout schematic design created in LineSim. I am using IBIS AMI models to configure the Tx and Rx. I have run a sweep over the length of trace in 3rd layer. The simulation is passing for PCIe Gen 4 for a trace length 3 inch, 10 inch and also for 20 inch. I have enabled the option to remove non-functional part in the via and also the back drilling in the via. I am using high loss FR4 (Dk = 4.7 and Df = 0.02) to the simulations. The height and width in the eye diagram reduces when using 20 inch long trace in 3rd layer but still passing the criteria for PCIe Gen 4. Is that a surprise ? as we know that FR4 is high loss dielectric material and dielectric losses dominates the conductor losses beyond 4 GHz approximately but then how it passes PCIe Gen 4 ?