alimassster

Junior Member level 3

Hi all

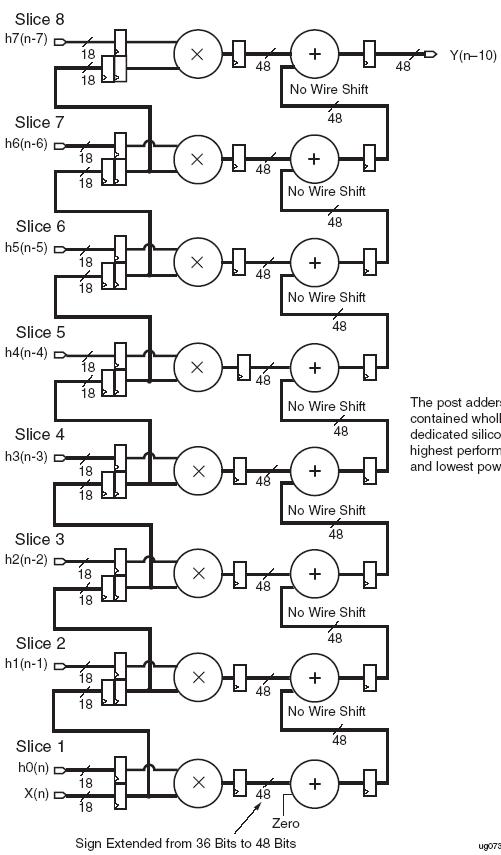

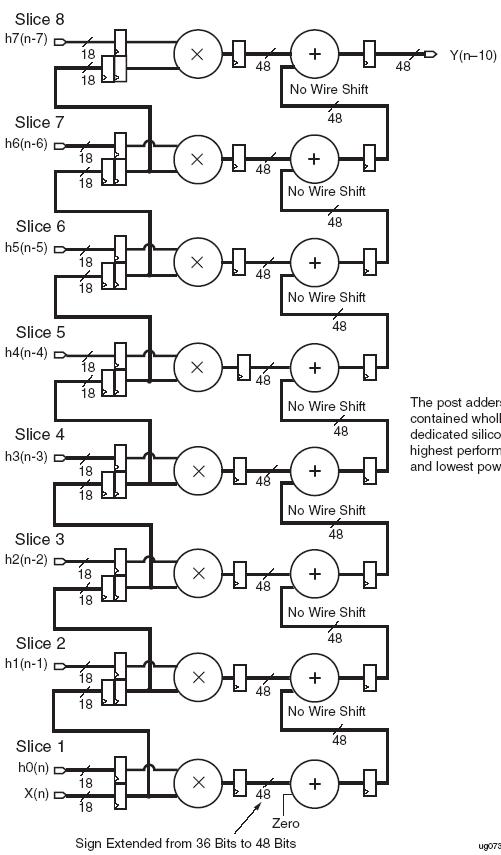

I wanna know by cascading DSP48 blocks if we need for example N clocks to feed multipliers with N inputs in an N tap FIR filter to calculate Y , then what's the difference between the parallel form and a single MACC based form ( if there's an equal delay(number of clocks) in both forms)?

what's the advantages of parallel implementation?

I know in parallel form we have a result in every clock cycle.

but is it because of useing pipeline or something else?

Are inputs ( not coeficients ) fed into multipliers simultaneously or one by one by using BCIN-BCOUT ? if so , again what's the advantage of a parallel form? is it using pipeline or what?

thx in adv

I wanna know by cascading DSP48 blocks if we need for example N clocks to feed multipliers with N inputs in an N tap FIR filter to calculate Y , then what's the difference between the parallel form and a single MACC based form ( if there's an equal delay(number of clocks) in both forms)?

what's the advantages of parallel implementation?

I know in parallel form we have a result in every clock cycle.

but is it because of useing pipeline or something else?

Are inputs ( not coeficients ) fed into multipliers simultaneously or one by one by using BCIN-BCOUT ? if so , again what's the advantage of a parallel form? is it using pipeline or what?

thx in adv