Shahed47

Newbie level 4

Hi,

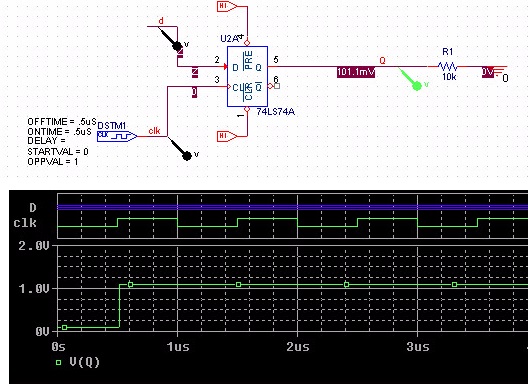

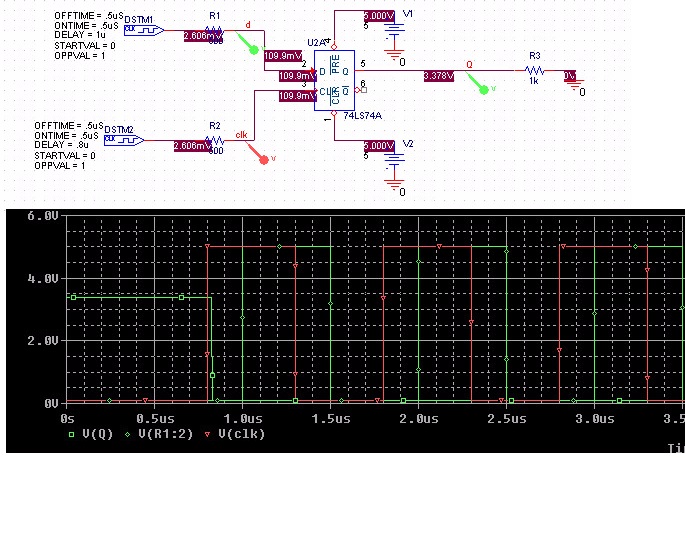

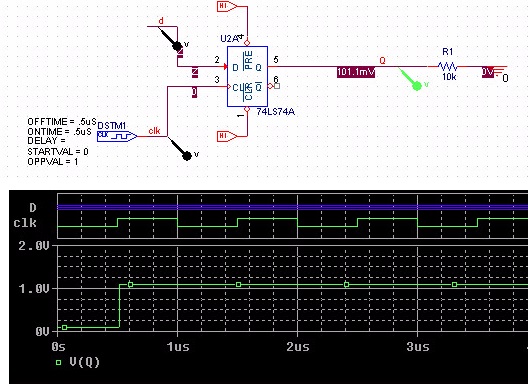

I am working on D flip-flip. Therefore, I tried to do simulation, it giving me output voltage when I am keeping the Input D floating or no voltage is applied to it. Could someone explain me what is the reason for it. Thanks in advance.

I am working on D flip-flip. Therefore, I tried to do simulation, it giving me output voltage when I am keeping the Input D floating or no voltage is applied to it. Could someone explain me what is the reason for it. Thanks in advance.