shaikss

Full Member level 4

Hi Folks,

I was going through some analytical paper on Opamps and got a doubt regarding the -ve feedback operation.

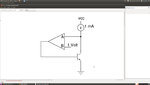

I have attached the circuit.

The Q is to label which of the terminals 'A' and 'B' are +ve and -ve so that the entire circuit works in -ve feedback.

Let me explain how I analysed the circuit,

Here terminal B is fixed to 1V and the current source of 1mA is driving the collector of BJT.

For me, it looks like a current monitor circuit.

So, I feel that the terminal which is connected to collector should be inverting terminal and so terminal A should be inverting terminal to make the circuit work in negative feedback mode.

Am I correct?

If wrong, Please correct me and let me know how to analyse the circuit.

Thanks!

I was going through some analytical paper on Opamps and got a doubt regarding the -ve feedback operation.

I have attached the circuit.

The Q is to label which of the terminals 'A' and 'B' are +ve and -ve so that the entire circuit works in -ve feedback.

Let me explain how I analysed the circuit,

Here terminal B is fixed to 1V and the current source of 1mA is driving the collector of BJT.

For me, it looks like a current monitor circuit.

So, I feel that the terminal which is connected to collector should be inverting terminal and so terminal A should be inverting terminal to make the circuit work in negative feedback mode.

Am I correct?

If wrong, Please correct me and let me know how to analyse the circuit.

Thanks!