ldhung

Member level 3

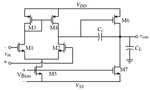

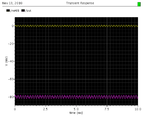

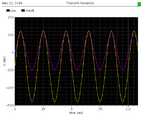

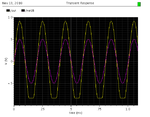

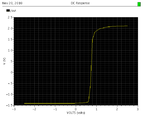

I designed an opamp unbuffered 2 stages, but there are the shifts between input and output. Please help me to adjust the output has the same offset is zero as input.

Please see the photos for more details.

Thanks

Please see the photos for more details.

Thanks