grabbo

Newbie level 6

Hello,

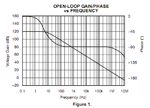

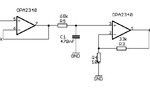

I would like to find out the stability of the circuit of an op amp ( OPA2340). I included phase/gain characteristics and the circuit. It's connected as a buffer and non inverting.

For non-inverting:

Gain=3.3. Feedback factor F=0.23. K=20log(0.23)= -12.77dB

Gain 0db crosses at around 6MHz. With K=0.23, it's shifted downward by -12.77dB to approximately 2Mhz. Phase is -100.

For buffer:

Gain=1 , K=0dB, Phase=-110.

Am i right in these assumptions? Those phases are phases margins or responses ?

Any suggestions?

I would like to find out the stability of the circuit of an op amp ( OPA2340). I included phase/gain characteristics and the circuit. It's connected as a buffer and non inverting.

For non-inverting:

Gain=3.3. Feedback factor F=0.23. K=20log(0.23)= -12.77dB

Gain 0db crosses at around 6MHz. With K=0.23, it's shifted downward by -12.77dB to approximately 2Mhz. Phase is -100.

For buffer:

Gain=1 , K=0dB, Phase=-110.

Am i right in these assumptions? Those phases are phases margins or responses ?

Any suggestions?