farid72j

Junior Member level 3

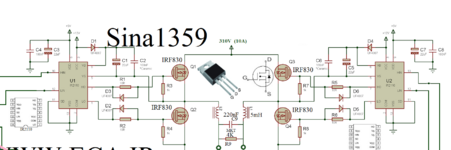

I have build a full bridge inverter using 2 IR2110 and 4 irf840 or 20n60 mosfets. pwm frequency of high side is 18 kHz and for the low side i use 50 Hz pulse. the circuit works fine with 25 and 50 volt from dc supply.

the problem is when i connect 310 v dc of rectifying 220 v ac to the circuit, 2 mosfet on one side burns instantly.

i use different mosfets and dead time up to 2 ms, the result is the same.

can someone tell me where is the problem?

thank you in advance.

the problem is when i connect 310 v dc of rectifying 220 v ac to the circuit, 2 mosfet on one side burns instantly.

i use different mosfets and dead time up to 2 ms, the result is the same.

can someone tell me where is the problem?

thank you in advance.