kinghero89

Junior Member level 2

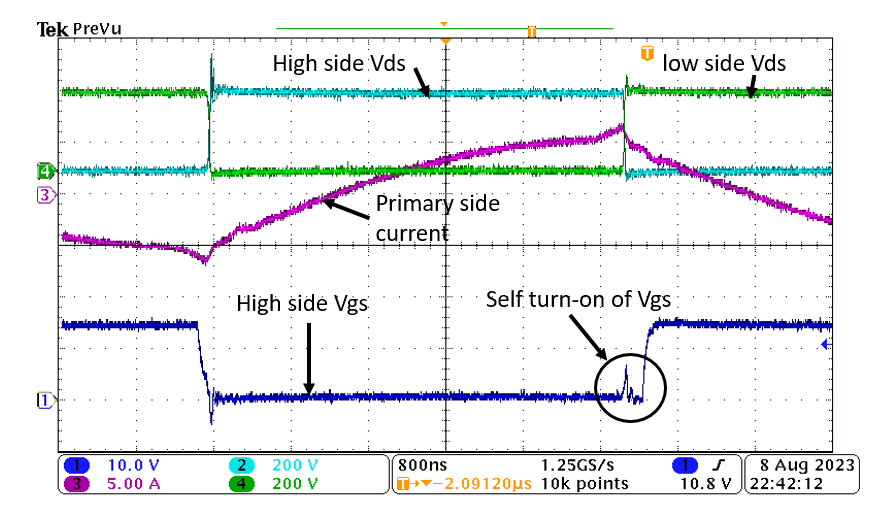

I am working on full-bridge CLLC, and the waveform I got is quite weird.

Is there anyone who has such kind of experience?

Is there anyone who has such kind of experience?

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

This is the schematic and gate driver I am usingLack of information

circuit topology? secondary rectifier or active bridge?

timing of low side gate signal?

gate driver strength?

do we see self commutation after low-side switch-off?

This happens at the active bridge, Thank you for your answerLack of information

circuit topology? secondary rectifier or active bridge?

timing of low side gate signal?

gate driver strength?

do we see self commutation after low-side switch-off?

thanks for your answer, the gate drive i am using has the maximum current up to 3AThis is a common experience for power electronics newbies, when the high side turns on the drain of the lower is pulled up rapidly, injecting current into the lower gate via Cgd

If the gate drive does not have a low Z to these high freq edges it cannot keep the Vgs down.

[ vice versa is true for high side GD when lower device turns on fast ]

I use MOSFET with Ciss = 1500pF and Cgd = 2.6pF, the maximum current of gate driver can be up to 3A as I posted earlierYou need Ciss >> Cgd. But also a powerful enough gate drive to hard short the gate to ground when the fet should be off.

But also, probe it with a homebrew coaxial probe because it could just be a common mode spike.

Beware isolation with a coaxial probe and your scope.

The standard scope "dangly ground" probe thing is good at producing fake artifacts that are really just common mode illusions.

The turn-on resistor is 12 Ohm, the turn-off resistor is 22 Ohm.Several questions are still open. Low side gate timing? Gate series resistors? Is it right that we see passive commutation after low side switch-off?

because i want to reduce the high dv/dt of Vds so i increase the Roff gate resistor. The phenomenon I mentioned occurs at the start of deadtime interval, when the primary current discharges the Vds voltage of the lower Mosfet rapidly may interfere the Vgs voltage of the upper Mosfet. Do you have any idea about it?I agree with Easy peasy. Problem is the inappropriately high Roff gate resistor. You really need strong gate clamping without negative gate voltage.

I am thinking of the parasitic inductanceyou appear to be missing the point, a simple diode S -> G would stop any neg spikes on the gate

it is the gate rise when the other device turns on that you should be concerned with

--- Updated ---

it is hard to see as you have not zoomed in - but the gate spike ( rise ) might be largely artifact too - due to probing. ( on your low side pictures )

Be careful about looking to simulations to investigate this sort of issue. There are many possible mechanisms for spikes (positive or negative) to appear where you're observing them. And in practice what we actually observe in real life is a combination of several mechanisms, not just one. So don't jump to conclusions just because LTspice showed something interesting.According to the simulation, the Vgs voltage spikes are negative. Do u guys have any idea?

You are right, you don't expect positive miller effect induced gate pulse when Vds is falling. It's more likely a measurement artifact, e.g. common mode error of the differential voltage probe. How do you exactly probe high side Vgs?According to the simulation, the Vgs voltage spikes are negative. Do u guys have any idea?

I am pretty sure there’s spikes. At the beginning, i thought it was the differential voltage probe error. I increased the load current to 4.5 A, the spike might be higher leading to self turn-on of Vgs and the Mosfet was broken.You are right, you don't expect positive miller effect induced gate pulse when Vds is falling. It's more likely a measurement artifact, e.g. common mode error of the differential voltage probe. How do you exactly probe high side Vgs?