jiaguoce

Newbie level 3

Hi,

I need to design a preamp for the comparator..

the input range is 1V, for a 12bits ADC, the offset should < 120uV.

assume the offset of the preamp is 10mV, to make it smaller than 120uV, now i plan to do the autozero, and in this case, a DC gain of the preamp should > 40dB, which means ios is the proper auto-zero method.

anyone here can help me to comfirm that whether it's right?

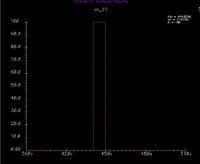

now i first need to meansure the offset of the preamp in cadence. i use the architecture in the figure(i find it from this forum), however there is no voltage difference between the two outputs.

then what's the method to meansure it?

thanks in advance

I need to design a preamp for the comparator..

the input range is 1V, for a 12bits ADC, the offset should < 120uV.

assume the offset of the preamp is 10mV, to make it smaller than 120uV, now i plan to do the autozero, and in this case, a DC gain of the preamp should > 40dB, which means ios is the proper auto-zero method.

anyone here can help me to comfirm that whether it's right?

now i first need to meansure the offset of the preamp in cadence. i use the architecture in the figure(i find it from this forum), however there is no voltage difference between the two outputs.

then what's the method to meansure it?

thanks in advance