Arnab1233

Newbie

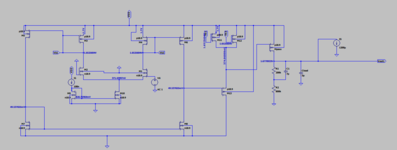

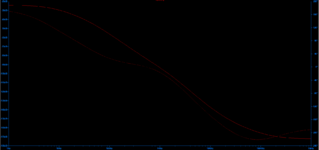

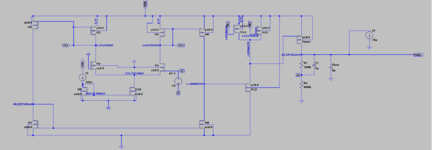

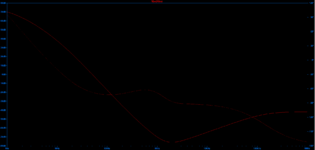

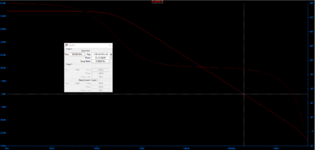

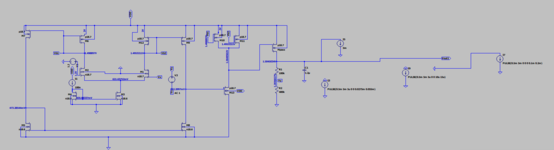

I am trying to design an LDO with the following specification: Vout = 1.5V; Vin = 1.7V - 2V; Iload = 75uA to 1200uA. However, while I am simulating its loop gain, its gain is coming negative. Even though all the transistors are in saturation within the given load condition. I have attached the testbench as well as the Bode Plot for it. Can anybody suggest what might be the reason?