Wall-eee

Newbie level 6

i'm currently working on my masters thesis where i have to design and implement a broadband UHF 50W Class AB PA single ended.

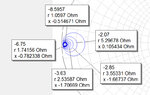

i was able to determine the optimum load and source impedance using loadpull simulations..my Zopt= 2 - j1.8

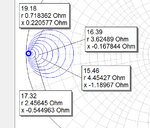

i'm now into my matching network designs at the input and output for my 50-ohm load and 50-ohm source. i'm using a 4 section LC network in this configuration.

using ideal LC parts, i get very good insertion and return losses (RL< -10, IL > -0.1)..then i progressively chance into real LC parts models (from ATC) then to changing inductor to transmission lines. the Insertion loss response are still acceptable but degraded to around -0.5dB for the whole UHF band.

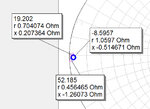

next i did a schematic (input matching network) to connect all the real LC parts with MLIN (from MWO) and configure such that it is close to my desired layout...using the closed form models and LC models, my IL response becomes very bad even after optimization. it is now in IL ~ -1.8dB..

i then tried to do Extraction in MWO (EM simulation) and even getting worse which is quite expected based.

i'm quite worried because when i go to output matching and i get this range of insertion losses, then my PA efficiency is very problematic..

any advise on my thesis problem?

i was able to determine the optimum load and source impedance using loadpull simulations..my Zopt= 2 - j1.8

i'm now into my matching network designs at the input and output for my 50-ohm load and 50-ohm source. i'm using a 4 section LC network in this configuration.

using ideal LC parts, i get very good insertion and return losses (RL< -10, IL > -0.1)..then i progressively chance into real LC parts models (from ATC) then to changing inductor to transmission lines. the Insertion loss response are still acceptable but degraded to around -0.5dB for the whole UHF band.

next i did a schematic (input matching network) to connect all the real LC parts with MLIN (from MWO) and configure such that it is close to my desired layout...using the closed form models and LC models, my IL response becomes very bad even after optimization. it is now in IL ~ -1.8dB..

i then tried to do Extraction in MWO (EM simulation) and even getting worse which is quite expected based.

i'm quite worried because when i go to output matching and i get this range of insertion losses, then my PA efficiency is very problematic..

any advise on my thesis problem?