OG_

Newbie level 6

Hello,

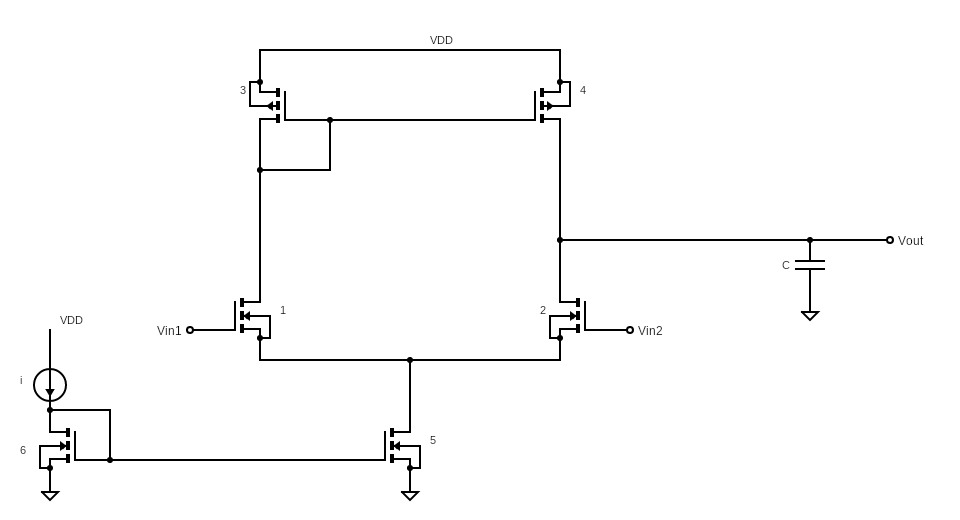

I am designing a diff amp in cadence virtuoso with the following architecture:

I am new to designing these amplifiers, so I started with noise/power constraints and worked my way from there. At the end of the day, I have the perfect AC response, gain is great, noise specs and power constraints are satisfied, AND it works across my input DC operating range. However, I performed a DC analysis around the bias points of my circuit that I was using on all previous analysis and I see none of the transistors are in saturation. In fact, some are even in the "0" range (which means cutoff according to this:https://community.cadence.com/cadence_technology_forums/f/custom-ic-design/14626/operating-region).

For a week I drove myself crazy trying to get the transistors in saturation, but inevitably, that would ruin one of the constraints I had.

My main question is this:

1. Based on this info, does it seem like one of my previous analysis were done incorrectly?

2. In industry, is it common to achieve all transistors in saturation in a diff amp design using 1.8V and super low power?

3. If transistors are not in saturation, what is something I should be super careful of/aware of? I think the main issue of not having transistors in saturation is that there would be non linearities based on the bias points.

Thank you! Let me know if you'd like any clarifications

I am designing a diff amp in cadence virtuoso with the following architecture:

I am new to designing these amplifiers, so I started with noise/power constraints and worked my way from there. At the end of the day, I have the perfect AC response, gain is great, noise specs and power constraints are satisfied, AND it works across my input DC operating range. However, I performed a DC analysis around the bias points of my circuit that I was using on all previous analysis and I see none of the transistors are in saturation. In fact, some are even in the "0" range (which means cutoff according to this:https://community.cadence.com/cadence_technology_forums/f/custom-ic-design/14626/operating-region).

For a week I drove myself crazy trying to get the transistors in saturation, but inevitably, that would ruin one of the constraints I had.

My main question is this:

1. Based on this info, does it seem like one of my previous analysis were done incorrectly?

2. In industry, is it common to achieve all transistors in saturation in a diff amp design using 1.8V and super low power?

3. If transistors are not in saturation, what is something I should be super careful of/aware of? I think the main issue of not having transistors in saturation is that there would be non linearities based on the bias points.

Thank you! Let me know if you'd like any clarifications