Junus2012

Advanced Member level 5

Dear friends

I have used the MOS as a capacitor. I am running it under the saturation strong inversion region.

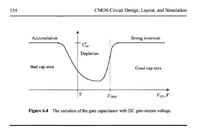

I have attached you this picture from Jakob Baker book. He told that in order to use the MOS a capacitor it must work in the strong inversion because it has less or no voltage dependency as shown in the graph.

However, the grph also shows the same stability in the accumulation region but the author told it is not good region to work as a capacitor. he didn't say why

But I am saying why ????

Please also to tell me the differences and the disadvantages between the MOS capacitor and the two parallel plate capacitor

Thank you in advance

I have used the MOS as a capacitor. I am running it under the saturation strong inversion region.

I have attached you this picture from Jakob Baker book. He told that in order to use the MOS a capacitor it must work in the strong inversion because it has less or no voltage dependency as shown in the graph.

However, the grph also shows the same stability in the accumulation region but the author told it is not good region to work as a capacitor. he didn't say why

But I am saying why ????

Please also to tell me the differences and the disadvantages between the MOS capacitor and the two parallel plate capacitor

Thank you in advance