natnoraa

Full Member level 1

Hi guys,

I know this could be a question in analog IC layout but since it's for rf/mm-wave domain, am thus seeking some advice here.

I have a rfline model from a pdk and from the process file, i see that it consists of the top most metal layer and a silicon substrate. Say I'm using a line of 100um and i find that the layout it's just a straight drawing of that 100um and it's too large.

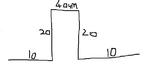

I would like to draw and simulate something like (it is a simplified sketch and the width is 4um):

1) can i do a drawing from cadence virtuoso layout suite and then export to hfss?

2) do i have to draw the return path (i assume it will be layer M1) in cadence or only when am simulating in HFSS?

3) do i have to use any vias (m1 all the way to the top most layer) to connect return path all the way to top most metal layer or they will be floating?

4) the path i've drawn, i assume both layers will be exactly identical and from the 3d point of view, the top most metal layer will just be on top of the bottom layer?

5) what's the gap in between the 2 layers we're looking at? foundry's limitation and process?

6) will the return path contribute to losses?

7) the layout generated from virtuoso will be exactly identical to what i've simulated in circuit simulation but not so from hfss?

8) after hfss simulation is done i'll export it back to cadence virtuoso?

If there's any guide you can point me to I will be glad to listen and learn. Thanks in advance!

Constraints: i only have a layer mapping tech file and amat files foundry provided for hfss. i can't simulate the components in hfss. only in cadence.

Natnoraa

I know this could be a question in analog IC layout but since it's for rf/mm-wave domain, am thus seeking some advice here.

I have a rfline model from a pdk and from the process file, i see that it consists of the top most metal layer and a silicon substrate. Say I'm using a line of 100um and i find that the layout it's just a straight drawing of that 100um and it's too large.

I would like to draw and simulate something like (it is a simplified sketch and the width is 4um):

1) can i do a drawing from cadence virtuoso layout suite and then export to hfss?

2) do i have to draw the return path (i assume it will be layer M1) in cadence or only when am simulating in HFSS?

3) do i have to use any vias (m1 all the way to the top most layer) to connect return path all the way to top most metal layer or they will be floating?

4) the path i've drawn, i assume both layers will be exactly identical and from the 3d point of view, the top most metal layer will just be on top of the bottom layer?

5) what's the gap in between the 2 layers we're looking at? foundry's limitation and process?

6) will the return path contribute to losses?

7) the layout generated from virtuoso will be exactly identical to what i've simulated in circuit simulation but not so from hfss?

8) after hfss simulation is done i'll export it back to cadence virtuoso?

If there's any guide you can point me to I will be glad to listen and learn. Thanks in advance!

Constraints: i only have a layer mapping tech file and amat files foundry provided for hfss. i can't simulate the components in hfss. only in cadence.

Natnoraa

Last edited: